[Digital Logic] Clock Gating 관련 용어

Clock gating은 현대 digital logic에서 power consumption 절감을 위해서 필수적인 scheme이다. Clock gating을 평가하기 위한 여러가지 지표가 있어서 이를 소개한다.

1. Clock Gating Ratio (CGR)

전체 register 중 clock-gated register의 비율을 나타낸다. 이상적인 값은 100%다.

2. Constant Inferred Clock Gating (CICG)

Clock gating cell의 input signal에 constant value로 tie 된 register의 비율을 나타낸다. 이상적인 값은 0% 이다.

3. Floating ICG (FICG)

ICG cell의 enable port에 input이 floating 된 register 의 비율을 나타낸다. 이상적인 값은 0% 이다.

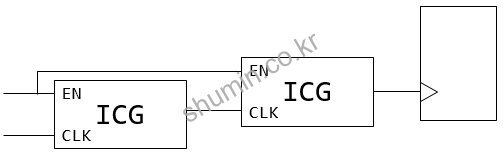

4. Redundant cascaded ICG (RICG)

ICG cell이 중복적으로 사용된 비율을 나타낸다. 이상적인 값은 0% 이다.

5. Memory Clock Gating Check (MCGC)

Clock gating이 적용 되지 않은 memory cell의 비율을 나타낸다. 이상적인 값은 0% 이다.

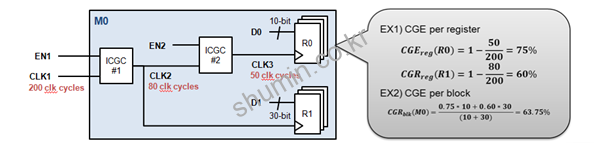

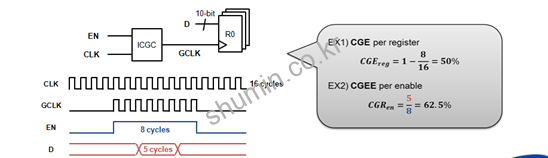

6. Clock Gating Efficiency (CGE)

Idle scenario에서 inferred clock gating의 gating efficiency를 나타내는 지표로, 계산식은 다음과 같다.

따라서 CGE의 값이 높으면 높을 수록 더 효과적으로 clock gating이 되는 design임을 나타낸다.

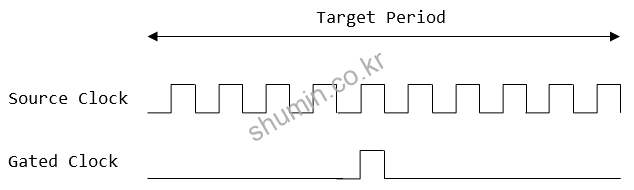

7. Clock Gating Enable Efficiency (CGEE)

Clock gating enable period동안 register의 valid한 data toggle cycle을 나타낸다. 즉, CGE는 idle state에서 clock gating이 얼마나 잘되는지를 보는 것이고, CGEE는 clock gating이 얼마나 유의미한 효과를 보이는지 나타낸다. 만약 clock gating이 되지 않은 상태에 data toggle이 되지 않는다면 불필요하게 clock이 들어오는 경우이기 떄문이다. CGEE의 이상적인 값은 100% 이다.