[Computer Arch.] TLB / Page Table

기본적으로 우리가 프로그램에서 사용하는 address는 모두 virtual address를 사용한다. 이러한 virtual address를 통해 physical address memory에 접근하는 기술을 virtual memory라 부른다. Virtual address의 장점은 다음과 같다.

- Multi process를 동시에 수행 할 때, address mapping만 각각하여 메모리를 효과적으로 공유한다.

- 32-bit OS 기준으로 4GB로 제한되는 memory space의 limitation을 넘는 memory space 영역을 사용할 수 있다.

- 서로 다른 process간 independent한 공간을 가지기 때문에 서로의 존재를 알 수 없어서 protection 기능이 있다.

이런 virtual memory system을 지원하기 위해선 크게 두 가지 logic들이 필요하다.

- Translate Lookup Table (TLB)

- Page Table

1. TLB

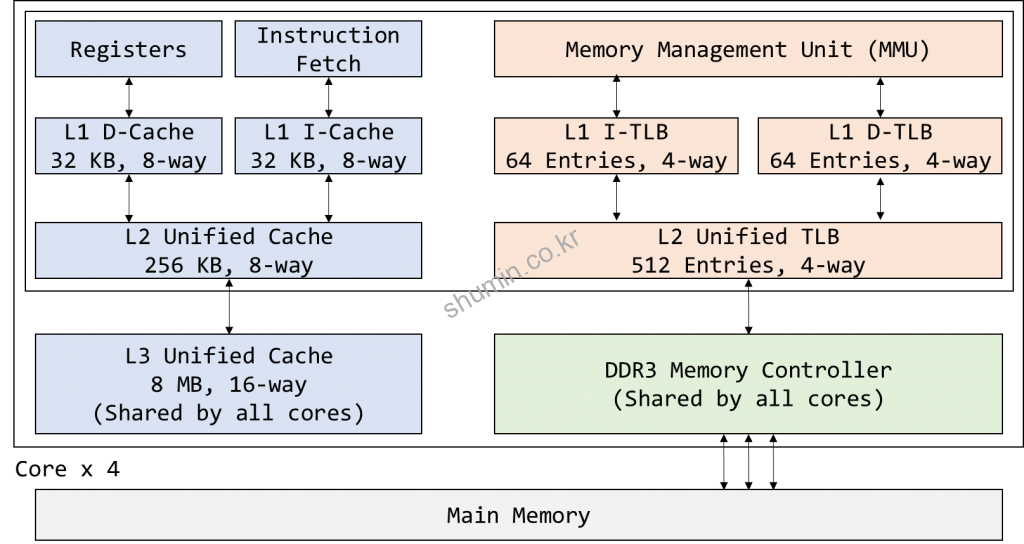

TLB는 각 cache별로 붙어있는 hardware logic으로 Page Table의 cache 버전이라고 생각하면 된다. 기본적으로 page table은 memory에 존재하는데, memory access까지 latency가 길기 때문에 각 core의 cache 근처 TLB access를 통해 빠르게 virtual address to physical address translation을 진행한다.

위 그림은 Intel의 Core i7 memory system의 block diagram이다. 위를 토대로 보면 MMU를 위한 cache (TLB)가 각 level별로 존재하는 것을 확인 할 수 있다. Memory access를 위한 다양한 scenario가 존재하겠지만 임의의 case를 설명하면 다음과 같다.

- Address translation (virtual address to physical address)를 위한 L1 TLB access

- L1 TLB miss로 인해 L2 TLB access

- L2 TLB miss로 인해 main memory에 있는 page table access

- Page table에서 valid한 entry 확인하여 L2 TLB로 load

- L2 TLB의 translation 정보를 L1 TLB로 load

- L1 TLB에 저장된 physical address를 통해 L1 cache access

- L1 cache miss로 인해 L2 cache access

- L2 cache miss로 인해 L3 cache access

- L3 cache miss로 인해 main memory access

만약 page table에서 valid entry가 존재하지 않으면 page fault가 발생하는데, 이 때는 storage (disk)에서 memory로 load가 필요하다. 그리고 참고로 segmentation fault는 physical address로 변환을 했음에도 불구하고 invalid address로 access가 될 경우에 발생된다.

2. Page Table

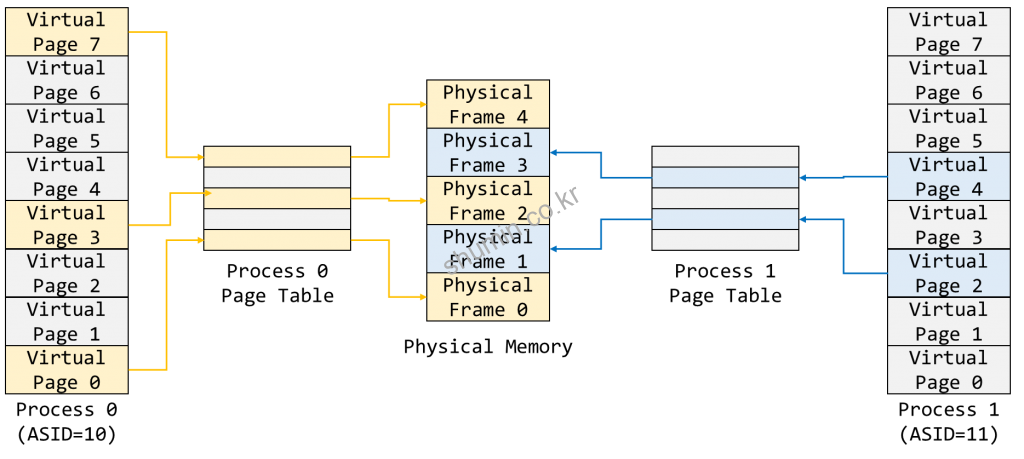

Page table은 virtual memory를 physical memory로 변환할 수 있는 정보를 담고 있는 데이터 구조다.

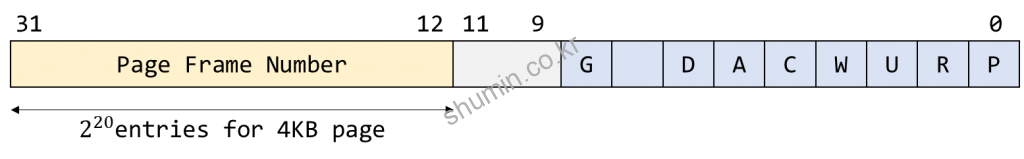

각 process별로 서로 다른 page table을 관리하며, 이들은 하나의 physical memory에 각기 다른 virtual memory address를 translation 해준다. 그리고 Page table entry 정보는 architecture마다 다를 수 있지만 대표적으로는 다음과 같다.

- G (Global): It prevents TLB from updating the address

- D (Dirty): Page was written

- A (Accessed): Page was read or written

- C (Cache disabled): Page will not be cached

- W (Write through): Write-through policy

- U (User/supervisor): Privilege level

- R (Read/write): Permission setting

- P (Present): Page is located in the physical memory

이런 virtual to physical address translation을 cache access 전후로 하는지에 따라 구조가 달라질 수 있다.

- Physically indexed, physically tagged cache

- Physically indexed, virtually tagged cache

- Virtually indexed, virtually tagged cache

- Virtually indexed, physically tagged cache

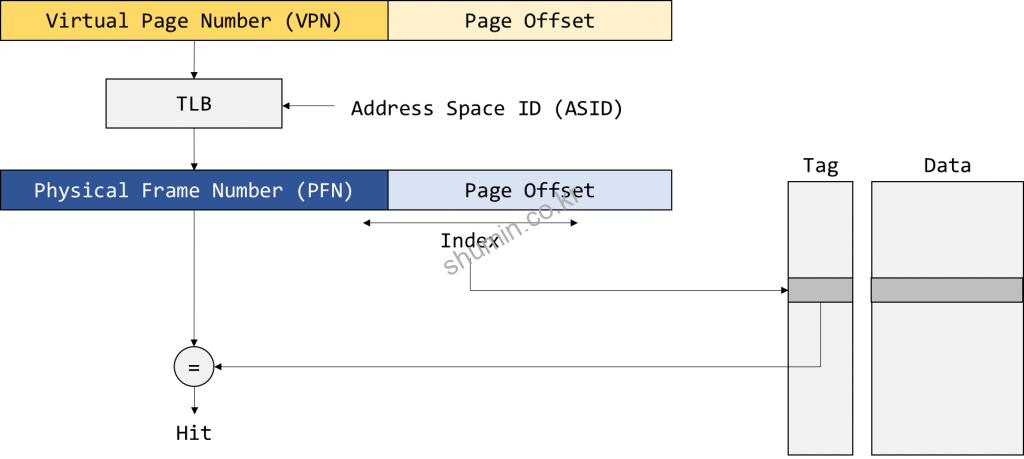

2.1 Physically indexed, physically tagged cache

위 구조는 cache access가 physical address로 translation 되고 난 뒤, physical indexed, physical tagged로 접근 되는 방식이다. 여기서 단점은 TLB access가 critical path가 될 수 있는 점이다.

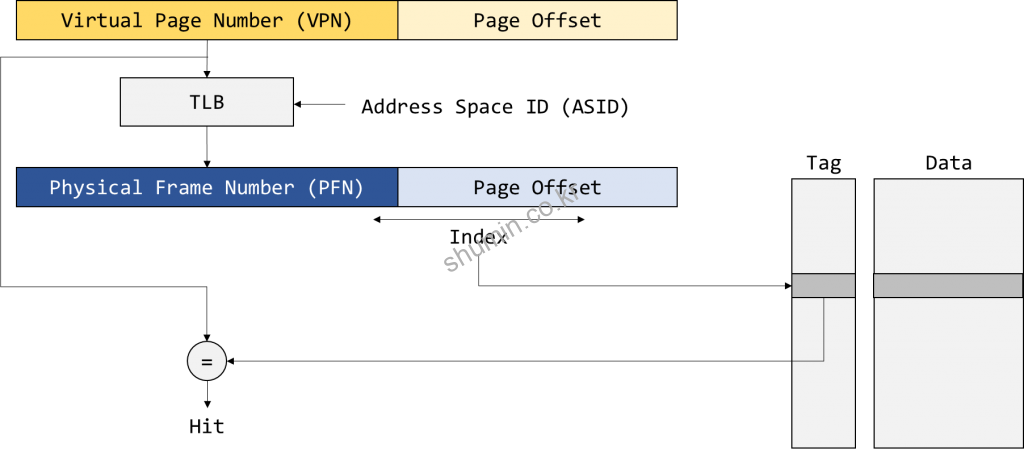

2.2 Physically indexed, virtually tagged cache

위 구조는 TLB access를 통해 PFN을 얻지 않은 채 cache access를 하는 경우인데, 여전히 TLB access를 통해 cache line index를 얻지만, tag matching 때 오직 virtual address만을 가지고 하기 때문에 valid data가 보장되지 않는 문제가 존재한다.

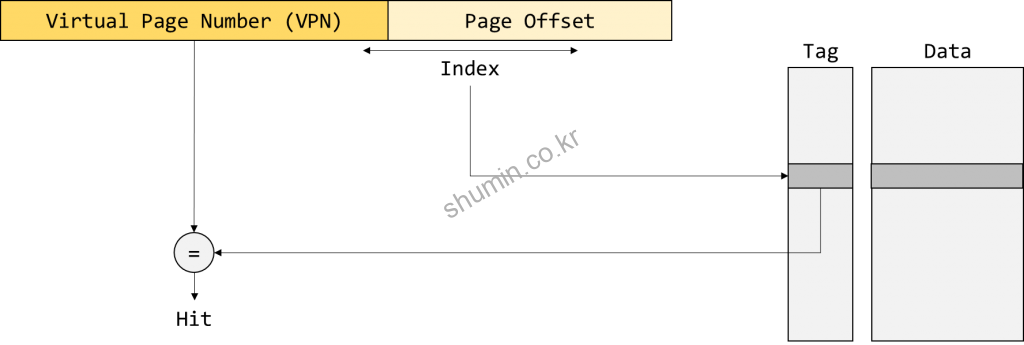

2.3 Virtually indexed, virtually tagged cache

위 경우는 오직 virtual address만을 가지고 cache access를 하는 경우다. 이 경우 또한 valid data를 보장하지 않는다.

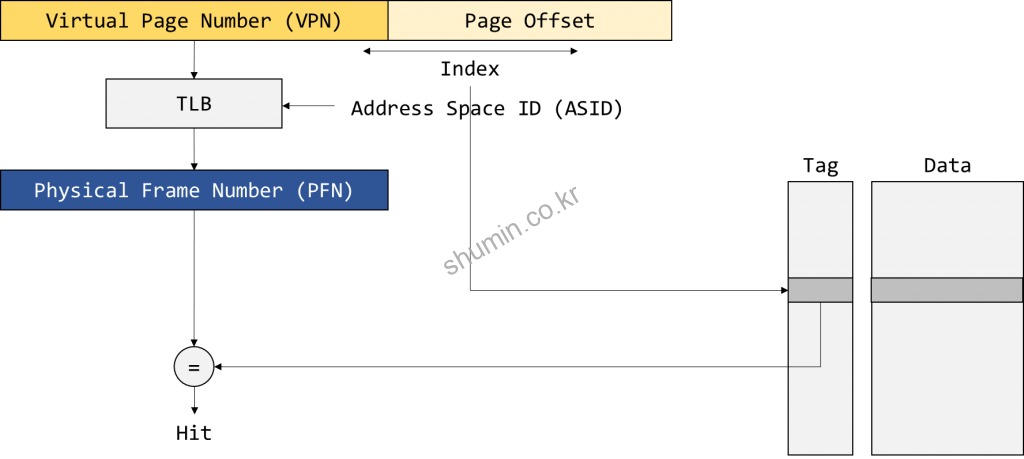

2.4 Virtually indexed, physically tagged cache

Cache entry indexing은 virtual address로 하면서 동시에 TLB access를 통해 physical address의 tag matching을 진행한다. 이런 경우 TLB access와 cache access가 병렬적으로 수행되기 때문에 성능 측면에서 효과적이다.

Reference

- https://about-myeong.tistory.com/35