Full Coherency vs. IO Coherency

Coherency Definition

Coherency의 정의는 하나의 시스템에 있는 모든 processor 또는 bus master들이 같은 memory view를 가지는 것을 의미한다. 특히 옛날과 다르게 요즘은 private cache를 사용하는 multi-core, heterogeneous system이 많기 때문에 더욱 중요해졌다. 그럼 coherency를 지원하기 위해선 어떻게 해야할까?

Mechanism to Contain Coherency

1. Disabling cache

가장 쉬운 방법으로 cache를 사용하지 않고, 모든 master unit들이 shared memory (대표적으로 DRAM)을 사용하는 것이다. 대신 높은 memory access latency로 인해 성능이 저하될 수 있다.

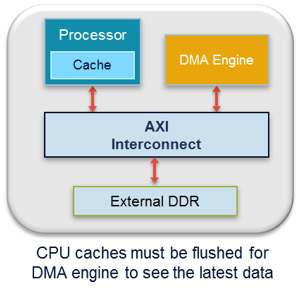

2. Software management

전통적인 shared data 문제를 해결하기위한 방법으로 device driver가 software level에서 각종 처리 (cache clean, cache invalidation 등)을 해주는 방법이다. 그러나 software level에서 하다보니 processor에게 많은 job들을 던져준다.

어떤 application vender는 이런 말을 했다고 한다.

“50% of debug time is spent on SW coherency issues as these are difficult to find and pinpoint.”

즉 SW에서 이런것까지 신경써줘야 하면 너무 힘들다는 말일 것이다.

3. Hardware management

Rough하게 말하면, Software에서 해주는 역할을 hardware로 구현해서 해주기 때문에 굳이 processor가 coherency를 위해 따로 동작할 필요가 없다.

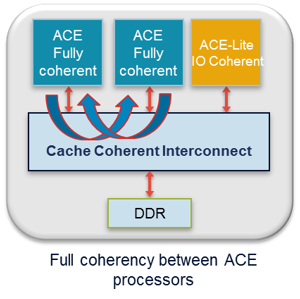

요즘은 multi-core 구조가 상용화되면서 이런 coherency protocol에 대한 연구가 많이 이뤄져왔다. Symmetric 구조 (동일한 구조의 코어)는 주로 full-coherency를 사용하고 Asymmetric 구조 (processor와 또 다른 device의 구조)에서 몇몇은 IO coherency를 사용한다.

Full Coherency

예를 들면 CPU와 GPU가 있는 구조가 있다고 하면, shared virtual memory를 가져서 GPGPU (General Purpose GPU)로서 활용 될 수 있다. 물론 이를 위해서 data를 서로 주고 받는 interface protocol 또한 지원을 해야한다. 대표적으로 AMBA ACEL가 있다.

여기서 구현 방식이 두 가지가 될 수 있는데 그 중 하나가 full coherency 방식이다. Full coherency의 경우 CPU와 GPU가 서로 같은 data를 동시에 보고 있다. 따라서 fine-grained cache의 status를 업데이트 해줄 필요가 있고, CPU와 GPU 모두 서로에 대해 snoop 기능이 필요하다.

참고로 snoop은 모니터링한다는 의미로, cache status가 바뀐지를 확인하여, 만약 해당 cache line state가 dirty (또 다른 master에 의해 업데이트가 되어 새로운 data fetch가 필요) 등으로 변한지를 확인해서 다음 동작을 진행한다.

추가적으로 atomic operation (같은 address에 대해서 쓰기/읽기가 발생 할 때 생기는 문제를 회피하기 위한 동작)이 지원되어야 한다.

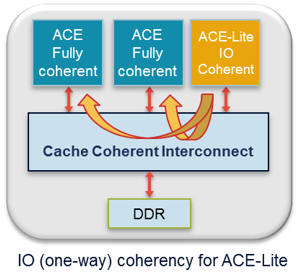

IO Coherency

만약 CPU의 cache에 있는 data를 GPU가 오직 보고 읽기 동작만 하면 full coherency가 아니라 IO coherency (one-way)가 지원되면 된다. GPU 뿐만 아니라 DMA, accelerator 등이 사용 될 때 IO coherency를 사용한다. 이때 cache를 쓰는 CPU가 아닌 다른 slave device들 (GPU, accelerator 등)이 snoop을 통해 CPU cache의 상태를 확인한다.

IO coherency를 위해서 ACE-Lite protocol이 개발되었다고 한다.

Reference

- https://community.arm.com/developer/ip-products/processors/b/processors-ip-blog/posts/extended-system-coherency—part-1—cache-coherency-fundamentals

- https://www.computer.org/publications/tech-news/heterogeneous-system-architecture/exploring-how-cache-coherency-accelerates-heterogeneous-compute