[Digital Logic] Static Timing Analysis (STA)

Definition

회로 설계하는 분야에서 Static timing analysis (STA)는 회로의 모든 타이밍 위배가 발생 할 수 있는 경로에 대해서 확인함으로서 성능을 검증하는 방법이다.

또 다른 검증 방법으론 dynamic simulation이 있는데, 이 방법은 모든 입력 벡터들에 대한 behavior를 돌려보고 확인하는 것이다. 상대적으로 STA에 비해 오랜 시간이 걸리는데, dynamic simulation은 테스트 벡터에 의해서 확인되기 때문에 놓치는 부분이 발생될 수 있다. 왜냐하면 gate delay, wire delay등이 모두 고려되지 않기 때문이다 (물론 #delay를 통해 할 수 있겠지만, 실제 합성된 net의 형태가 결정되지 않기 때문에 쉽지 않다). 대신 STA는 functionality는 확인이 안되는 부분이 단점이다.

How to Work

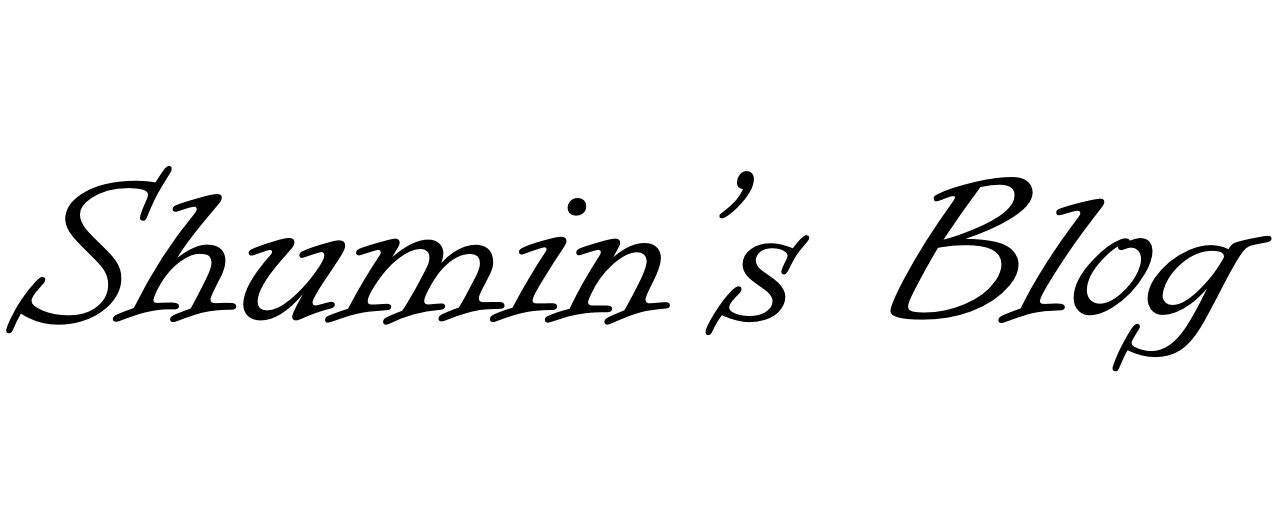

일반적인 회로는 sequential logic + combinational logic의 조합으로 구성되며, 매 clock 마다 새로운 값이 sequential logic에 저장이 된다. 따라서 모든 시작은 sequential logic의 output으로부터 시작해 sequential logic의 input으로 끝난다.

Startpoint: clock의 edge로부터 시작

Combinational logic network: AND, OR와 같은 값을 저장하는 sequential logic이 아닌 logic들을 의미한다. 실제 STA 중 data path로 구성되는 combinational logic들 path 중 가장 긴 path delay들의 값을 기준으로 STA를 수행한다.

Endpoint: clock의 edge로 capture되는 flip-flop의 clock port 또는 latch의 G port

Timing Analysis

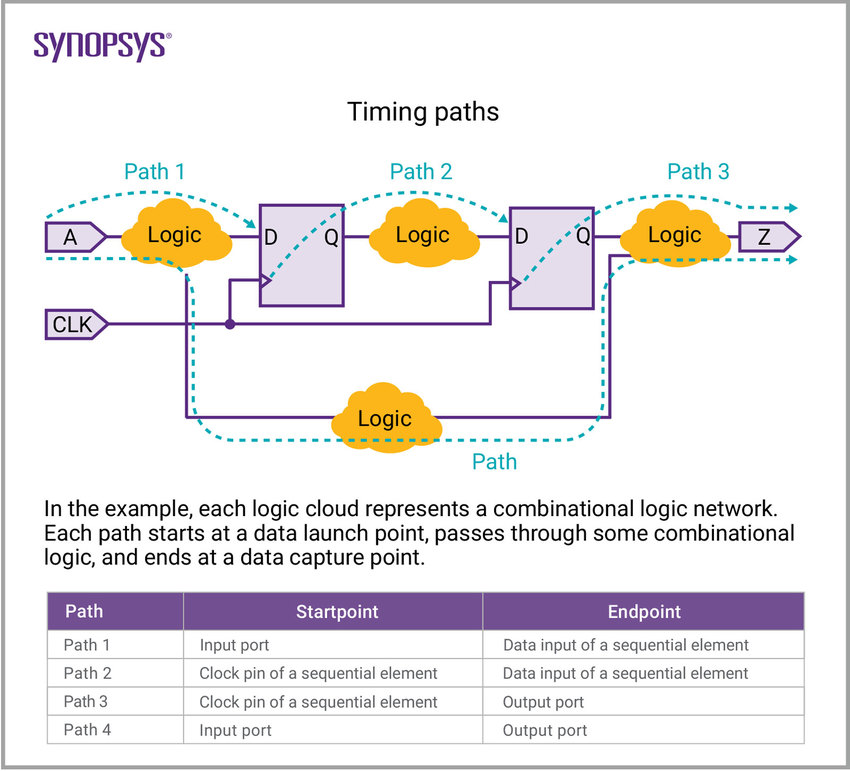

Clock path: flip-flop의 clock port로 연결되기 위한 clock path로, 중간에 buffer들을 통해 연결되며 setup / hold time을 측정하는데 사용됨

Clock-gating path: clock을 항상 toggling하게 되면 불필요한 power가 소비되기 때문에 실제 사용될 때만 clock이 입력되도록 AND logic등을 통해 gating해주게 된다.

Asynchronous path: sequential element의 set 또는 reset을 연결해주는 path를 의미하며 asynchronous circuit에서 모든 path를 의미한다.

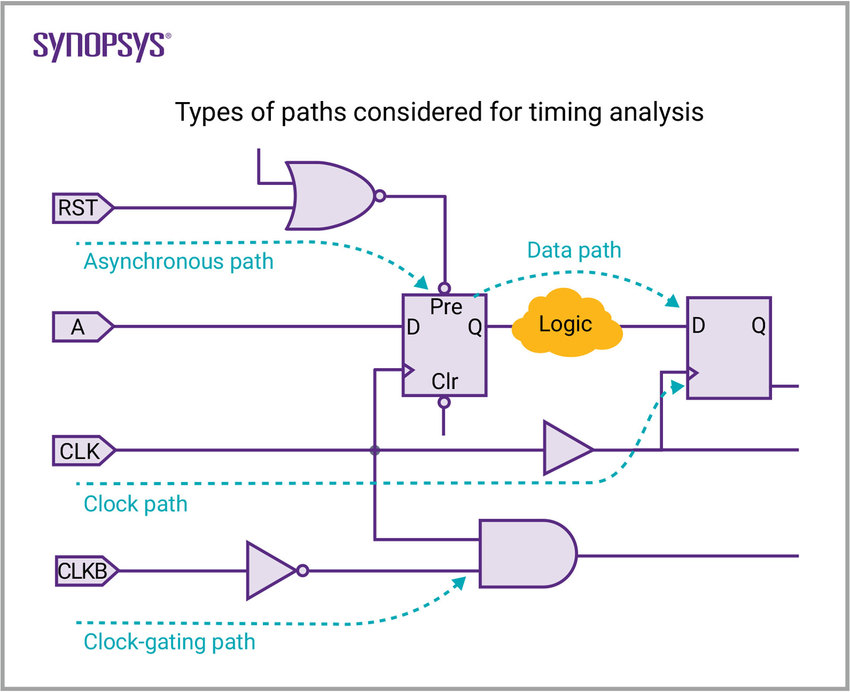

Setup time: clock의 rising edge가 발생하기 전, 즉 data capture가 일어나기 전에 data가 미리 도착해야되는 시간을 의미한다. Setup time을 만족하는지 확인하기 위해 data path 중 max delay path와 clock 1 cycle과 비교를 해서 더 작은지를 확인해야한다. (max data path delay + setup time < clock period + clock skew)

Hold time: clock의 rising edge가 발생하고 난 뒤 data capture를 위한 최소한의 시간동안 유지해야되는 시간을 의미한다. Hold time을 만족하는지 확인하기 위해 data path 중 min delay path와 이전 flip-flop의 clock path delay과 비교해서 더 큰지를 확인해야한다. (min data path delay > clock skew + hold time)

False path: timing이 고려되지 않는 path를 말한다. 예를 들면 MUX의 A와 B가 있다면 그 둘은 절대 동시에 사용될 수 없는데, 이를 false path라고 부를 수 있다. 또 다른 예시로는 synchronizer가 있다.

False path로 고려해야할 path를 false path로 세팅하지 않을 경우, timing 상에서 절대로 constraint를 맞출 수 없으므로 해당하는 path들에서 violation이 발생한다. (Run time을 줄이기 위해서도 사용한다.)

Multi-cycle path: 만약 clock period에 맞춰 setup time을 만족시키기 어려 울 때, 2 cycle에 맞춰 동작시키도록 하는 방식이다. 이 때 모든 path가 1 cycle period보다 길고 2 cycle period보다 짧아야한다.

Reference

- https://www.synopsys.com/glossary/what-is-static-timing-analysis.html

- https://m.blog.naver.com/yeonnim0930/221963916830

- https://www.edn.com/equations-and-impacts-of-setup-and-hold-time/